Cygnet

Overview

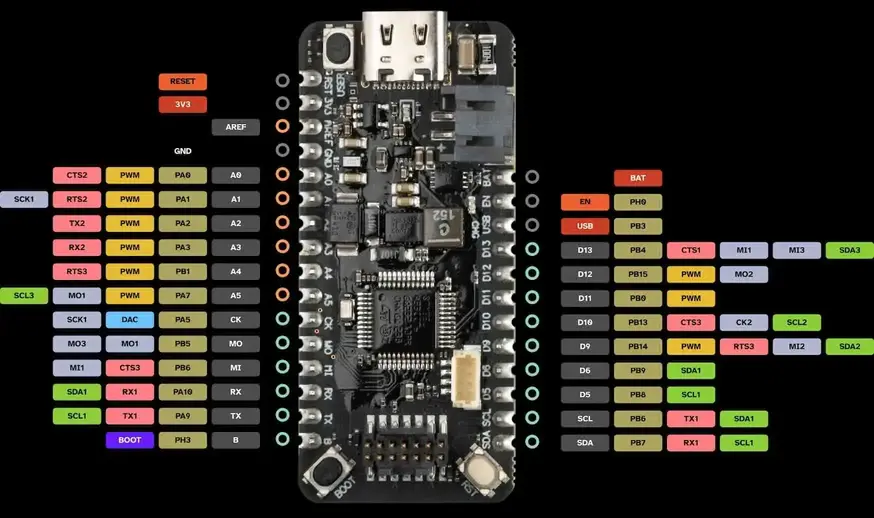

The Blues Cygnet board features an ARM Cortex-M4 based STM32L433CC MCU with a wide range of connectivity support and configurations. Here are some highlights of the Cygnet board:

STM32L4 microcontroller in LQFP48 package

Adafruit Feather connector

User LED

User push-button

USB Type-C connector

More information about the board can be found at the Blues Cygnet website [1].

Hardware

The STM32L433CC SoC provides the following hardware IPs:

Ultra-low-power with FlexPowerControl (down to 28 nA Standby mode and 84 µA/MHz run mode)

Core: ARM® 32-bit Cortex®-M4 CPU with FPU, frequency up to 80 MHz, 100DMIPS/1.25DMIPS/MHz (Dhrystone 2.1)

Clock Sources:

32 kHz crystal oscillator for RTC (LSE)

Internal 16 MHz factory-trimmed RC (±1%)

Internal low-power 32 kHz RC (±5%)

Internal multispeed 100 kHz to 48 MHz oscillator, auto-trimmed by LSE (better than ±0.25 % accuracy)

2 PLLs for system clock, USB, audio, ADC

RTC with HW calendar, alarms and calibration

11x timers:

1x 16-bit advanced motor-control

1x 32-bit and 2x 16-bit general purpose

2x 16-bit basic

2x low-power 16-bit timers (available in Stop mode)

2x watchdogs

SysTick timer

Up to 21 fast I/Os, most 5 V-tolerant

Memories

Up to 256 KB single bank Flash, proprietary code readout protection

64 KB of SRAM including 16 KB with hardware parity check

Rich analog peripherals (independent supply)

1x 12-bit ADC 5 MSPS, up to 16-bit with hardware oversampling, 200 µA/MSPS

2x 12-bit DAC output channels, low-power sample and hold

1x operational amplifiers with built-in PGA

2x ultra-low-power comparators

17x communication interfaces

USB 2.0 full-speed crystal less solution with LPM and BCD

1x SAI (serial audio interface)

3x I2C FM+(1 Mbit/s), SMBus/PMBus

4x USARTs (ISO 7816, LIN, IrDA, modem)

1x LPUART (Stop 2 wake-up)

3x SPIs (and 1x Quad SPI)

CAN (2.0B Active)

14-channel DMA controller

True random number generator

CRC calculation unit, 96-bit unique ID

Development support: serial wire debug (SWD), JTAG, Embedded Trace Macrocell*

More information about STM32L433CC can be found here:

Supported Features

The cygnet board supports the hardware features listed below.

- on-chip / on-board

- Feature integrated in the SoC / present on the board.

- 2 / 2

-

Number of instances that are enabled / disabled.

Click on the label to see the first instance of this feature in the board/SoC DTS files. -

vnd,foo -

Compatible string for the Devicetree binding matching the feature.

Click on the link to view the binding documentation.

cygnet/stm32l433xx target

Type |

Location |

Description |

Compatible |

|---|---|---|---|

CPU |

on-chip |

ARM Cortex-M4F CPU1 |

|

ADC |

on-chip |

STM32 ADC2 |

|

CAN |

on-chip |

STM32 CAN controller1 |

|

Clock control |

on-chip |

STM32 RCC (Reset and Clock controller)1 |

|

on-chip |

STM32 HSE Clock1 |

||

on-chip |

|||

on-chip |

STM32 MSI Clock1 |

||

on-chip |

STM32 LSE Clock1 |

||

on-chip |

|||

on-chip |

STM32 Microcontroller Clock Output (MCO)1 |

||

Counter |

on-chip |

STM32 counters6 |

|

CRC |

on-chip |

STM32 CRC calculation unit1 |

|

DAC |

on-chip |

STM32 family DAC1 |

|

DMA |

on-chip |

STM32 DMA controller (V2)2 |

|

Flash controller |

on-chip |

STM32 Family flash controller1 |

|

GPIO & Headers |

on-chip |

STM32 GPIO Controller6 |

|

on-board |

GPIO pins exposed on Adafruit Feather headers1 |

||

I2C |

on-chip |

||

I2S |

on-chip |

STM32 SAI controller2 |

|

Input |

on-board |

Group of GPIO-bound input keys1 |

|

Interrupt controller |

on-chip |

ARMv7-M NVIC (Nested Vectored Interrupt Controller)1 |

|

on-chip |

STM32 External Interrupt Controller1 |

||

LED |

on-board |

Group of GPIO-controlled LEDs1 |

|

Memory controller |

on-chip |

STM32 Battery Backed RAM1 |

|

MMC |

on-chip |

STM32 SDMMC Disk Access1 |

|

MTD |

on-chip |

STM32 flash memory1 |

|

on-board |

Fixed partitions of a flash (or other non-volatile storage) memory1 |

||

NVMEM |

on-chip |

Fixed layout for Non-Volatile memory1 |

|

OTP memory |

on-chip |

||

PHY |

on-chip |

This binding is to be used by all the usb transceivers which are built-in with USB IP1 |

|

Pin control |

on-chip |

STM32 Pin controller1 |

|

Power management |

on-chip |

STM32 power controller1 |

|

PWM |

on-chip |

||

QSPI |

on-chip |

STM32 QSPI Controller1 |

|

Regulator |

on-board |

Fixed voltage regulators1 |

|

Reset controller |

on-chip |

STM32 Reset and Clock Control (RCC) Controller1 |

|

RNG |

on-chip |

STM32 Random Number Generator1 |

|

RTC |

on-chip |

STM32 RTC1 |

|

Sensors |

on-chip |

STM32 quadrature decoder2 |

|

on-chip |

STM32 family TEMP node for production calibrated sensors with two calibration temperatures1 |

||

on-chip |

STM32 VREF+1 |

||

on-chip |

STM32 VBAT1 |

||

Serial controller |

on-chip |

STM32 USART3 |

|

on-chip |

STM32 LPUART1 |

||

SMbus |

on-chip |

STM32 SMBus controller3 |

|

SPI |

on-chip |

||

Timer |

on-chip |

ARMv7-M System Tick1 |

|

on-chip |

|||

on-chip |

STM32 low-power timer (LPTIM)2 |

||

USB |

on-chip |

STM32 USB controller1 |

|

Watchdog |

on-chip |

STM32 watchdog1 |

|

on-chip |

STM32 system window watchdog1 |

Note

CAN feature requires a CAN transceiver.

Connections and IOs

The Cygnet board has 6 GPIO controllers. These controllers are responsible for pin muxing, input/output, pull-up, etc.

Available pins

For more details please refer to Blues Cygnet User Manual [2].

Default Zephyr Peripheral Mapping

LPUART_1_TX : PB11

LPUART_1_RX : PB10

UART_1_TX : PA9

UART_1_RX : PA10

I2C_1_SCL : PB6

I2C_1_SDA : PB7

PWM_2_CH1 : PA0

SPI_1: SCK/MISO/MOSI : PA5/PA6/PB5

System Clock

The Cygnet board System Clock could be driven by internal or external oscillator, as well as main PLL clock. By default System clock is driven by PLL clock at 80MHz, driven by 16MHz high speed internal oscillator.

Serial Port

The Cygnet board has 4 U(S)ARTs and 1 LPUART. The Zephyr console output is assigned to LPUART1. Default settings are 115200 8N1.

Programming and Debugging

The Cygnet board requires an ST-LINK embedded debug tool in order to be programmed and debugged.

Applications for the cygnet board configuration can be built and

flashed in the usual way (see Building an Application and

Run an Application for more details).

Flashing

The board is configured to be flashed using west STM32CubeProgrammer [5] runner, so its installation is required.

Alternatively, OpenOCD or JLink can also be used to flash the board using

the --runner (or -r) option:

$ west flash --runner openocd

$ west flash --runner jlink

Flashing an application to Cygnet

Connect the Cygnet to the ST-LINK debugger, then run a serial host program to connect with your Cygnet board.

$ picocom /dev/ttyACM0 -b 115200

Now build and flash an application. Here is an example for Hello World.

# From the root of the zephyr repository

west build -b cygnet samples/hello_world

west flash

You should see the following message on the console:

$ Hello World! cygnet

Debugging

You can debug an application in the usual way. Here is an example for the Hello World application.

# From the root of the zephyr repository

west build -b cygnet samples/hello_world

west debug