RA6E1 Fast Prototyping Board

Overview

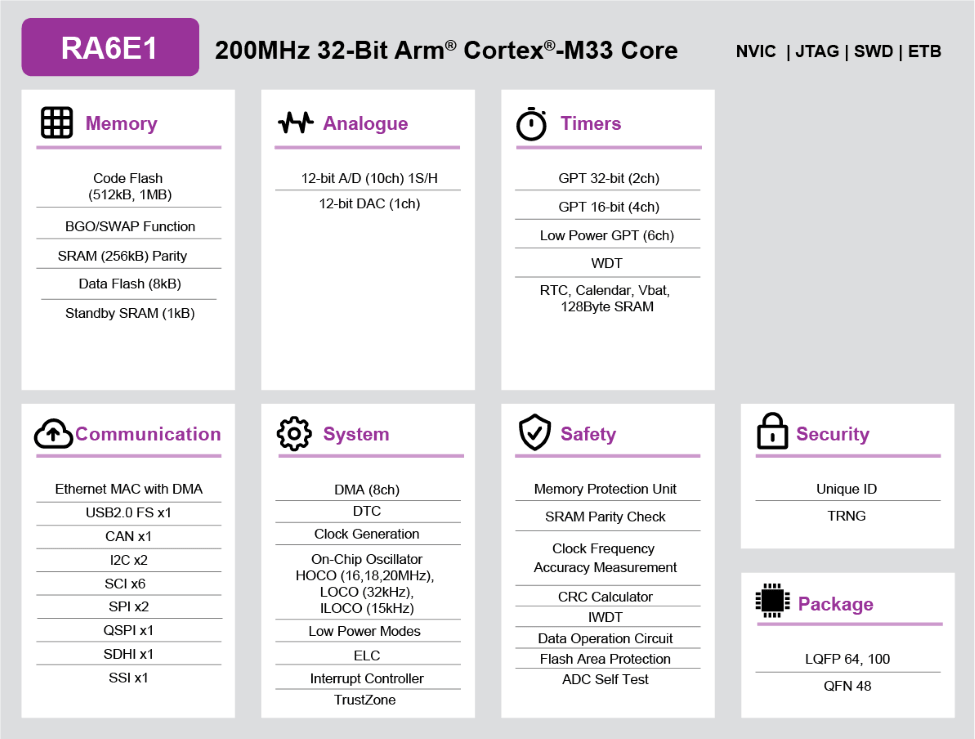

The Renesas RA6E1 group uses the high-performance Arm® Cortex®-M33 core with TrustZone®. The RA6E1 is suitable for entry IoT applications requiring streamlined feature and connectivity integration including Ethernet, and unprecedented performance with 790.75 CoreMark, which are 3.95CoreMark / Mhz.

The key features of the FPB-RA6E1 board are categorized in three groups as follow:

MCU Native Pin Access

200MHz Arm Cortex-M33 based RA6E1 MCU in 100 pins, LQFP package

Native pin access through 2 x 50-pin male headers (not fitted)

MCU current measurement point for precision current consumption measurement

Multiple clock sources - Low-precision (~1%) clocks are available internal to the RA MCU. RA MCU oscillator and sub-clock oscillator crystals, providing precision 24.000 MHz (not fitted) and 32,768 Hz reference clocks are also available

System Control and Ecosystem Access

Two 5V input sources

USB (Debug, Full Speed, High Speed)

External power supply (using 2-pin header) (not fitted)

Built-in SEGGER J-Link Emulator On-Board programmer/debugger (SWD)

User LEDs and buttons

Two User LEDs (green)

Power LED (green) (not fitted) indicating availability of regulated power

Debug/power LED (yellow) indicating power and the debug connection

One User button

One Reset button

Two popular ecosystems expansions

Two Digilent PmodTM (SPI, UART) connectors (not fitted)

Arduino (Uno R3) connector

MCU boot configuration jumper

Hardware

Detailed hardware features for the RA6E1 MCU group can be found at RA6E1 Group User’s Manual Hardware

RA6E1 Block diagram (Credit: Renesas Electronics Corporation)

Detailed hardware features for the FPB-RA6E1 MCU can be found at FPB-RA6E1 - User’s Manual

Supported Features

The fpb_ra6e1 board supports the hardware features listed below.

- on-chip / on-board

- Feature integrated in the SoC / present on the board.

- 2 / 2

-

Number of instances that are enabled / disabled.

Click on the label to see the first instance of this feature in the board/SoC DTS files. -

vnd,foo -

Compatible string for the Devicetree binding matching the feature.

Click on the link to view the binding documentation.

fpb_ra6e1/r7fa6e10f2cfp target

Type |

Location |

Description |

Compatible |

|---|---|---|---|

CPU |

on-chip |

ARM Cortex-M33 CPU1 |

|

ADC |

on-chip |

Renesas RA 12-bit resolution ADC (ADC12)1 |

|

Clock control |

on-chip |

Renesas RA Clock Generation Circuit external clock configuration1 |

|

on-chip |

Generic fixed-rate clock provider3 |

||

on-chip |

Renesas RA Sub-Clock1 |

||

on-chip |

|||

on-chip |

Renesas RA Clock Control node pclk block1 |

||

on-chip |

|||

Counter |

on-chip |

Renesas RA AGT as Counter6 |

|

CRC |

on-chip |

Renesas RA CRC device1 |

|

DAC |

on-chip |

Renesas RA DAC Controller Global1 |

|

on-chip |

Renesas RA DAC Controller1 |

||

DMA |

on-chip |

Renesas RA DMA Controller1 |

|

Ethernet |

on-chip |

Renesas RA Ethernet1 |

|

on-chip |

Renesas RA External MDIO controller1 |

||

Flash controller |

on-chip |

Renesas RA family flash high-performance controller1 |

|

GPIO & Headers |

on-chip |

||

I2C |

on-chip |

||

on-chip |

Renesas RA SCI I2C controller4 |

||

Input |

on-chip |

Renesas RA Capacitive Sensing Unit1 |

|

on-board |

Group of GPIO-bound input keys1 |

||

Interrupt controller |

on-chip |

ARMv8-M NVIC (Nested Vectored Interrupt Controller)1 |

|

LED |

on-board |

Group of GPIO-controlled LEDs1 |

|

Miscellaneous |

on-chip |

Renesas RA Event Link Controller1 |

|

on-chip |

|||

on-chip |

Renesas RA AGT6 |

||

on-chip |

|||

MMU / MPU |

on-chip |

ARMv8-M MPU (Memory Protection Unit)1 |

|

MTD |

on-chip |

Flash memory binding for Renesas RA Code flash region1 |

|

on-chip |

Flash memory binding for Renesas RA Data flash region1 |

||

on-board |

Fixed partitions of a flash (or other non-volatile storage) memory1 |

||

PHY |

on-chip |

This binding is to be used by all the usb transceivers which are built-in with USB IP1 |

|

Pin control |

on-chip |

Renesas RA Pin Controller1 |

|

PWM |

on-chip |

||

QSPI |

on-chip |

Renesas RA QSPI1 |

|

RNG |

on-chip |

Renesas RA SCE9 TRNG1 |

|

Serial controller |

on-chip |

||

SPI |

on-chip |

Renesas RA SCI SPI controller6 |

|

on-chip |

|||

SRAM |

on-chip |

Generic on-chip SRAM1 |

|

Timer |

on-chip |

ARMv8-M System Tick1 |

|

USB |

on-chip |

Renesas RA USB full-speed controller1 |

|

on-chip |

Renesas RA USB device controller1 |

||

Watchdog |

on-chip |

Renesas RA Watchdog (wdt)1 |

Programming and Debugging

The fpb_ra6e1 board supports the runners and associated west commands listed below.

| flash | debug | debugserver | attach | rtt | reset | |

|---|---|---|---|---|---|---|

| jlink | ✅ (default) | ✅ (default) | ✅ | ✅ | ✅ | ✅ |

| pyocd | ✅ | ✅ | ✅ | ✅ | ✅ |

Applications for the fpb_ra6e1 board target configuration can be

built, flashed, and debugged in the usual way. See

Building an Application and Run an Application for more details on

building and running.

Flashing

Program can be flashed to FPB-RA6E1 via the on-board SEGGER J-Link debugger. SEGGER J-link’s drivers are available at https://www.segger.com/downloads/jlink/

To flash the program to board

Connect to J-Link OB via USB port to host PC

Make sure J-Link OB jumper is in default configuration as describe in FPB-RA6E1 - User’s Manual

Execute west command

west flash -r jlink

Debugging

You can use Segger Ozone (Segger Ozone Download) for a visual debug interface

Once downloaded and installed, open Segger Ozone and configure the debug project like so:

Target Device: R7FA6E10F

Target Interface: SWD

Target Interface Speed: 4 MHz

Host Interface: USB

Program File: <path/to/your/build/zephyr.elf>

Note: It’s verified that we can debug OK on Segger Ozone v3.30d so please use this or later version of Segger Ozone